# **IT2200J**

The IT2200J employs an analogue ASIC for the oscillator and a high order temperature compensation circuit in a 2.5 x 2.0 mm size package. The device can be placed in power down mode through a single input pin. During standard operation, power consumption is minimised by operating down to a supply voltage of 1.8 to 3.3V.

The IT2200J's high stability, low power consumption, small footprint and powerful compensation method makes it a TCXO ideally suited for demanding GNSS mobile applications.

#### **Features**

- Excellent phase noise performance

- Low start up drift rate

- Power down mode

- Standard temperature stability of ±0.5 ppm over wide temperature ranges

## **Applications**

- Time and frequency reference

- GNSS

- Smartphone

- Communications

- Consumer

### 2.5 x 2.0 mm

## **Standard Specifications**

| Parameter                                | Min. | Тур.      | Max.          | Unit   | Test Condition / Description                                                                                                                                      |

|------------------------------------------|------|-----------|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nominal frequency                        |      | 10 - 52   |               | MHz    |                                                                                                                                                                   |

| Frequency calibration                    |      |           | ±1            | ppm    | Offset from nominal frequency measured at 25°C ±2°C                                                                                                               |

| Reflow shift                             |      |           | ±1            | ppm    | Two consecutive reflows as per attached profile after 2 hours relaxation at 25°C                                                                                  |

| Operating temperature range              | -40  |           | 85            | °C     | The operating temperature range over which the frequency stability is measured                                                                                    |

| Frequency stability over temperature     |      |           | ±0.5          | ppm    | Referenced to the midpoint between minimum and maximum frequency value over the specified temperature range <sup>1</sup> .  Control voltage set to midpoint of Vc |

| Frequency slope                          |      |           | ±0.05 -<br>±1 | ppm/°C | Minimum of one frequency reading every 2°C over the operating temperature range <sup>1</sup>                                                                      |

| Static temperature hysteresis            |      |           | 0.6           | ppm    | Frequency change after reciprocal temperature ramped over the operating range. Frequency measured before and after at 25°C                                        |

| Sensitivity to supply voltage variations |      |           | ±0.1          | ppm    | V <sub>DD</sub> varied ±5% at 25°C                                                                                                                                |

| Sensitivity to load variations           |      |           | ±0.2          | ppm    | ±10% load change at 25°C                                                                                                                                          |

| Long term stability                      |      |           | ±1            | ppm    | Frequency drift over 1 year at 25°C                                                                                                                               |

| Supply voltage (V <sub>DD</sub> )        |      | 1.8 – 3.3 |               | V      | With a tolerance of ±5%                                                                                                                                           |

| Supply current                           |      |           | 2.2           | mA     | At minimum V <sub>DD</sub> <sup>2</sup>                                                                                                                           |

| Output waveform                          |      |           |               |        | DC coupled clipped sine wave <sup>3</sup>                                                                                                                         |

| Output voltage level                     | 0.8  |           |               | V      | At minimum supply voltage <sup>2</sup>                                                                                                                            |

| Output load                              |      | 10        |               | kΩ/pF  | 10 kΩ //10 pF ±10%                                                                                                                                                |

| Start-up time (amplitude)                |      |           | 0.5           | ms     | Within 90% of the minimum specified output level                                                                                                                  |

| Start-up time (frequency)                |      |           | 2             | ms     | Within ±0.5 ppm of steady state frequency                                                                                                                         |

<sup>&</sup>lt;sup>1</sup> Parts should be shielded from drafts causing unexpected thermal gradients. Temperature changes due to ambient air currents on the oscillator can lead to short term frequency drift.

<sup>&</sup>lt;sup>2</sup> Specified for load stated in oscillator output section at 25°C.

<sup>&</sup>lt;sup>3</sup> External AC-Coupling capacitor required. 1 cp

nF or greater recommended.

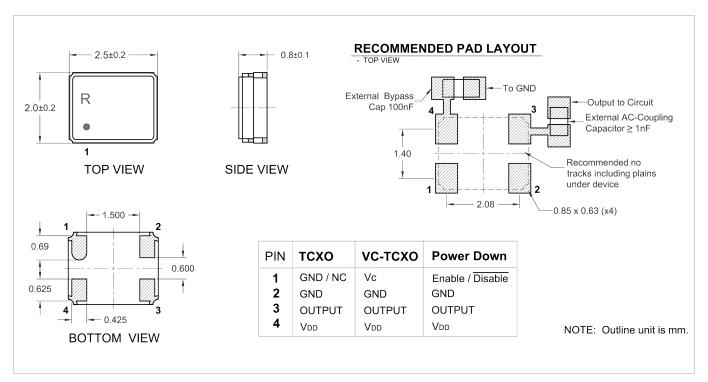

### **Model Outline and Recommended Pad Layout**

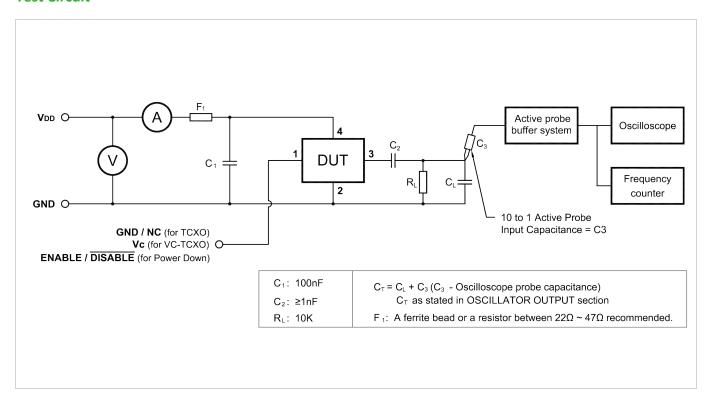

### **Test Circuit**